许居衍院士:复归于道——封装改道芯片业

1 前言

“历史事件犹如枝上嫩芽,总在它要长出的地方露头,结出果子。”

2003 年,x86 cpu 升级到64 位,由于登纳德等效缩放(dennard equivalent scaling)失灵,时钟频率止步于4 ghz。为降低功耗、提高算力,处理器分别于2006、2010 年进入了多核和异构计算时代,从而为异构封装打通了增长的快车道。2016 年发生了两起不同而又相关的事件:以摩尔定律(moore’s law)为指导的“国际半导体技术路线图(international technology roadmap for semiconductors,简称itrs)”,在ieee“重启计算倡议”的协同下,更换为“国际器件与系统路线图(international roadmap for devices and systems,简称irds)”,权威刊物nature 指出“半导体行业将很快放弃摩尔定律”;与此同时,苹果iphone 7 上搭载集成多核cpu 和多个gpu 的a10 处理器,采用了台积电(tsmc)的集成扇出(info)先进封装技术。而就在这一年,晶圆级封装技术(wlp)在经过多年平缓增长后猛增一倍,从2015 年的244 亿美元增加到500 亿美元,并从此高速增长。

这些事件表明,提出多年的“拓展摩尔”(more than moore)终于在“后摩尔时代”迎来了高潮。异构/异质集成激发了多芯片封装(mcp)/多芯片模组(mcm)的发展,有望在当前芯片产业基础上催生新的产业生态系统和新的商业模式。

2 摩尔时代,单片集成驱动soc 辉煌过后面临问题

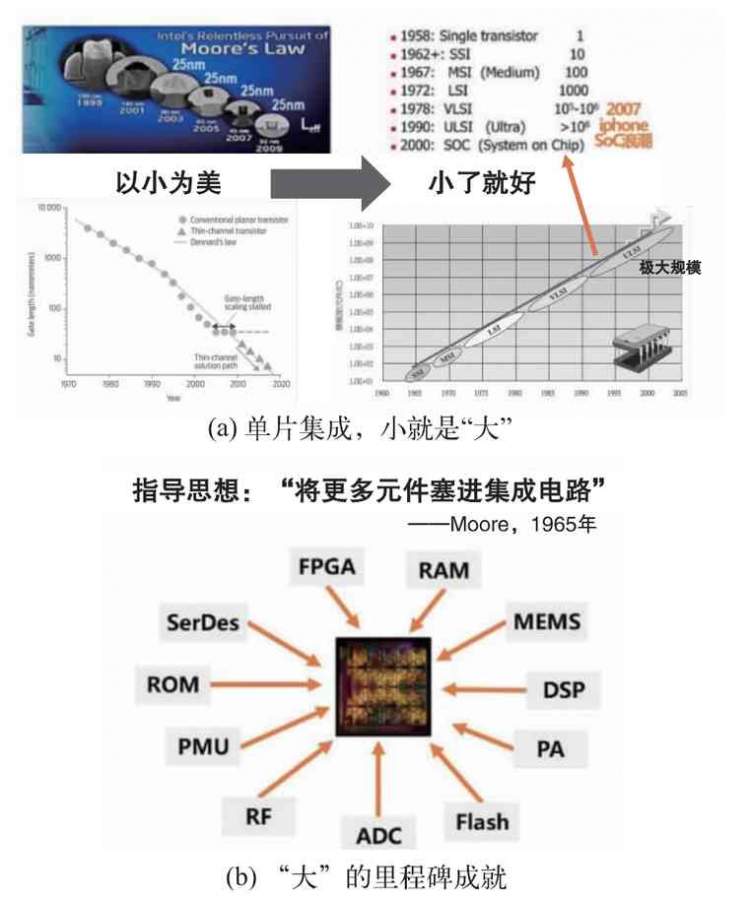

1965 年,戈登·摩尔(gordon moore)以“把更多元件塞进集成电路里”为题,发表在electronics 上的这句话,一直被半导体界奉为圭臬。晶体管越做越小、功能越加越多、规模越来越大,如图1 所示。

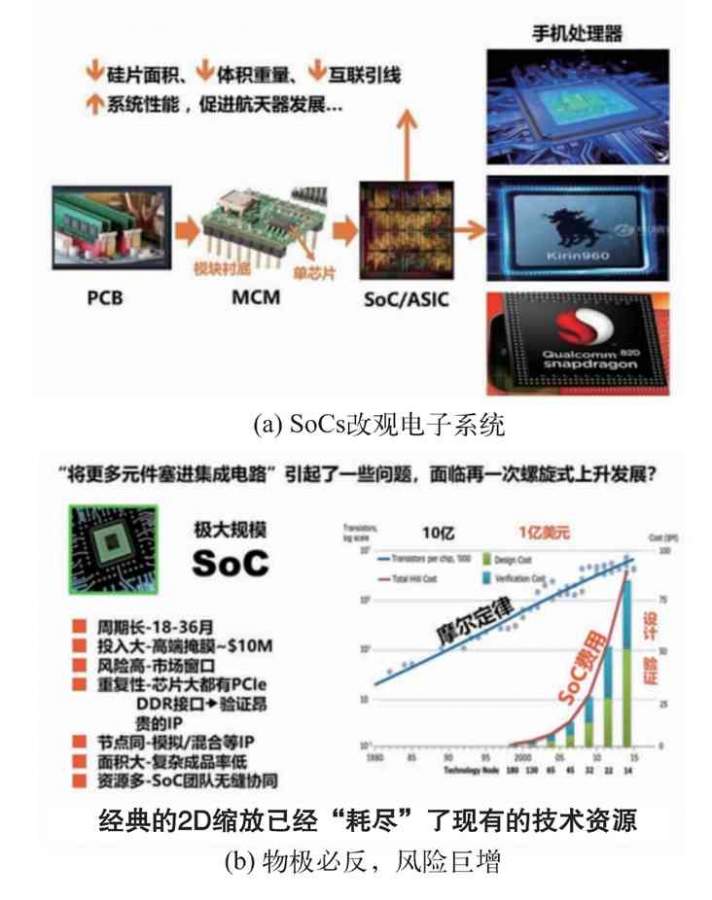

soc(系统级芯片)是半导体技术发展历程中的一个重大里程碑,它在提高产品性能、增加产品功能和可靠性的同时,还大幅缩短了产品开发周期、降低了开发成本;更为重要的是,soc 不仅仅是一个软件和硬件的集成子系统,而且还是一个技术平台,极大地改观了传统的电子信息系统。

但是,“物极必反”,将更多元件塞进集成电路带来周期长(18~36 个月)、投入大、风险高、面积大、复杂度高、仿真与验证耗时长,以及重复性(芯片大都有pcie ddr 接口)和多资源要求(soc 团队无缝协同)等问题,使得制程进一步微缩所需要的研发经费呈指数级增长,制造工艺所要求的高端掩模的价格急剧攀升,极端复杂的集成度不仅需要庞大的soc 团队无缝协同,还进一步拉低了芯片良率,盈利风险愈发明显。总之,经典的2d 缩放已经“耗尽”了现有的技术资源,需要另找出路,如图2 所示。

3 后摩尔时代,多片集成、芯粒模式或将驱动未来

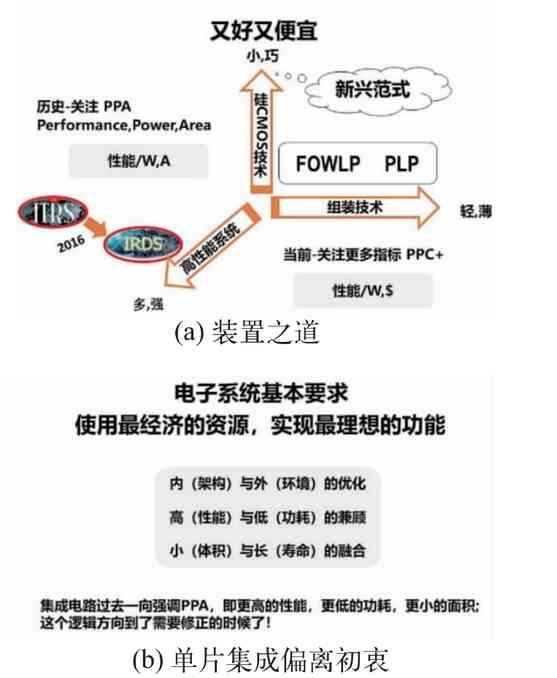

“装置之道”在于“又好又便宜”,如图3 所示。过去,单片集成讲的是ppa(性能、功耗、面积),强调的是面积,而电子系统的基本要求是使用最经济的资源,实现最理想的功能。这包括内架构与外环境的优化、高性能与低功耗的兼顾、小体积与长寿命的融合。而无休止地追求单片集成,尤其在摩尔定律日薄西山的后摩尔时代,工艺节点的进一步缩小,并不能带来集成元件成本和集成芯片性能翻番的好处;特别是对于需要靠近计算元件的高带宽存储(hbm)、需要不同且最佳工艺节点的非数字、非硅的模拟、传感和光电子的功能模块则更是无能为力。而后者恰恰是多片堆叠的异构封装的长处,它不仅可以提高性能,而且还能降低成本、提高成品率。

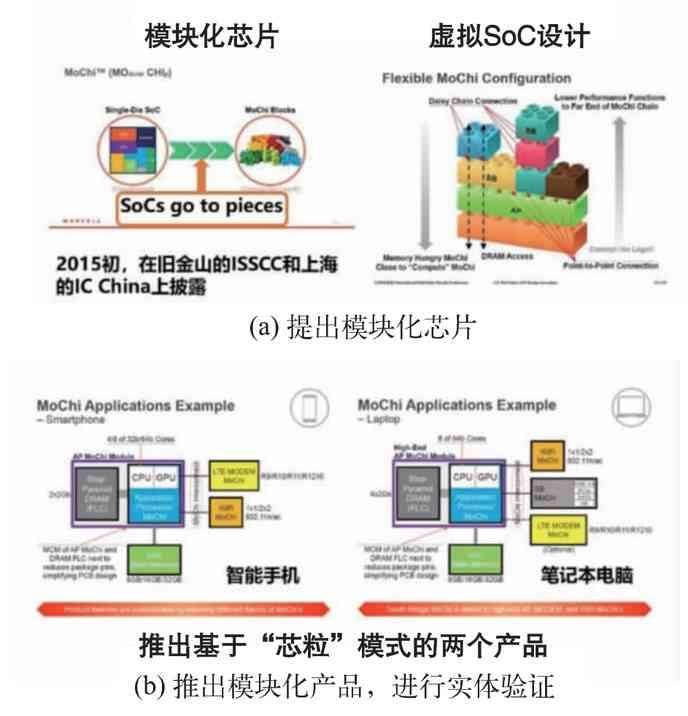

2016 年是一个颇有意思的年份,在irds 替代itrs 的同时,wlp 进入市场转折点(据yole développement 报告),迎来了3d 异构/异质封装的规模化商用。特别是人工智能(异构、类脑芯片)、5g(gan 器件)、iot(传感器)等应用的发展,大大推动了“拓展摩尔”在后摩尔时代的主角作用。在这种趋势下,一些大型芯片制造商正在开始转向“分割”原来“塞进”复杂soc 中的某些模块,如serdes、pa、存储单元等等,逐个做成裸管芯,然后再通过先进封装组装成产品。2015 年,marvell 提出以mochitm 为商标命名的模块化芯片概念,并以智能手机和笔记本电脑处理器为例,推出两款采用mochitm 方法的验证产品,如图4所示。

2017 年,美国国防部高级研究计划局(darpa)在电子复兴计划(eri)中启动了名为“通用异构集成及知识产权复用策略(chips)”的项目,旨在打造离散的、适当节点制造的多样化芯粒(chiplet)生态系统,开发模块化芯片并将之(和其他异质元件)组装成更大系统(模块)的设计工具、集成标准和ip 块;参与单位包括大型微电子公司(英特尔、美光等)、半导体设计公司(cadence、synopsys 等)、大型防务公司(洛克希德·马丁、波音等)、大学(密歇根大学等)。darpa 的这一举动得到了多方响应。2018 年10 月,7 家公司成立odsa(open domain-specific architecture)组织,到今年上半年就增加到53 家,其目标是制定芯粒开放标准、促进形成芯粒生态系统。英特尔目前已经创建了自己的生态系统并正在着力推动建立芯粒行业标准,如推出高密度互连的嵌入式多芯片互连桥(emib)和可作为行业标准接口的高级接口总线(aib)技术,还发布了名为foveros 的全新3d 异质堆叠技术。

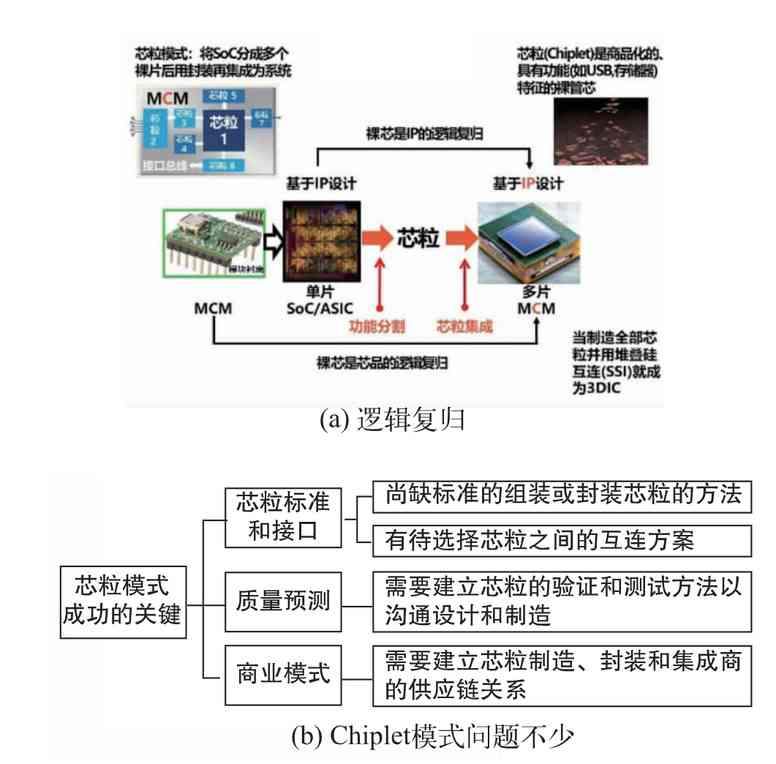

从这里,我们看到一个“螺旋上升、复归于道”的过程:芯粒是商品化的、具有特定功能(如usb、存储器)的、未经封装的裸芯片(硬ip);制造全部芯粒并用堆叠硅互连(ssi)就成为了3d ic。芯粒模式就是硬ip 的复用,是传统soc 的软ip 复用的“复归”,而由芯粒搭积木组装的“多芯片模组(mcm)”则是传统成品芯片“mcm”的逻辑复归,如图5 所示。

当前odsa 组织正在推动芯粒接口与标准,未来不论芯粒来自台积电、中芯国际还是世界其他厂商,都能根据需要合理选择并“即插即用”,从而推动微系统的整体发展、推进芯片架构创新、加快系统架构创新、加速领域专用架构与语言(dsa/dsl)、可重构计算的发展以及软件定义系统的发展。将芯粒与多片异构集成封装技术完美结合,像搭积木一样制造芯片将可能改变计算行业。

芯粒模式成功的关键在于芯粒的标准和接口,目前仍然面临诸多难题,如行业尚缺标准的组装或封装芯粒的方法,芯粒之间的互连方案有待选择,需要建立芯粒的验证和测试方法以沟通设计和制造,还需要建立芯粒制造、封装和集成商的供应链关系等等;不同节点设计制成的芯粒在集成时所采用的拓扑结构也面临不少难题。值得欣慰的是,国内的封测企业如长电、通富微电、华天、华进等在先进封装领域已有长足发展,未来成就可期。

4 结束语

英特尔公司一位专家宣称,芯粒模式兴起“即将迎来多芯片封装(mcp)的海啸”,国外一些大型芯片制造商纷纷转向芯粒,对于业界来说,这是个积极的信号。“封装改道芯片业”或将成为现实。若干年后是否会形成一个开放的产业生态,是否要建立芯粒生态推进联盟也是值得业界认真思考的问题。

目前,国内idm、fabless、foundry 厂商还很少关注芯粒的发展,而芯粒模式又涉及产业链的各个方面,本次年会提出的“协同发展、共享共赢”的会议主旨,对于健康发展芯粒生态具有重要的意义。

(本文由赵博、季鹏飞根据许居衍院士在2019 中国半导体封装测试技术与市场年会上的报告整理)

doi:10.16257/j.cnki.1681-1070.2019.1001

收稿日期:2019-09-21

作者简介:

许居衍(1934—),男,中国工程院院士,中国电子科技集团公司第五十八研究所名誉所长,长期从事半导体技术与工业的开发工作,研制成功中国第一代单片硅平面集成电路制造技术,曾获全国科学大会奖、国防科技进步奖,部、省级科技进步奖多项。

图1 单片集成哲学.jpg

图2 soc 的成就与当前风险.jpg

图3 单片集成偏离“装置之道”.jpg

图4 marvell 试水多片集成.jpg

图5 芯粒逻辑复归与面临问题.jpg![]() 返回小木虫查看更多

返回小木虫查看更多

京公网安备 11010802022153号

京公网安备 11010802022153号

电子封装技术专业 哭了

感动的吗

,

为什么被屏蔽了欧